DDR學習心得(一)

前言

最近在學習DDR3/DDR4相關知識,從中總結了一些心得,想放在CSDN上記錄下來。之前在CSDN上看了不少大神的貼文,對我的學習頗有幫助,現在我也想把我的學習程序記錄下來,希望可以和各位大神進行技術交流。這也是我第一次寫技術文章,如有錯誤還請各位及時指正

一、SDRAM介紹及DDR3的結構

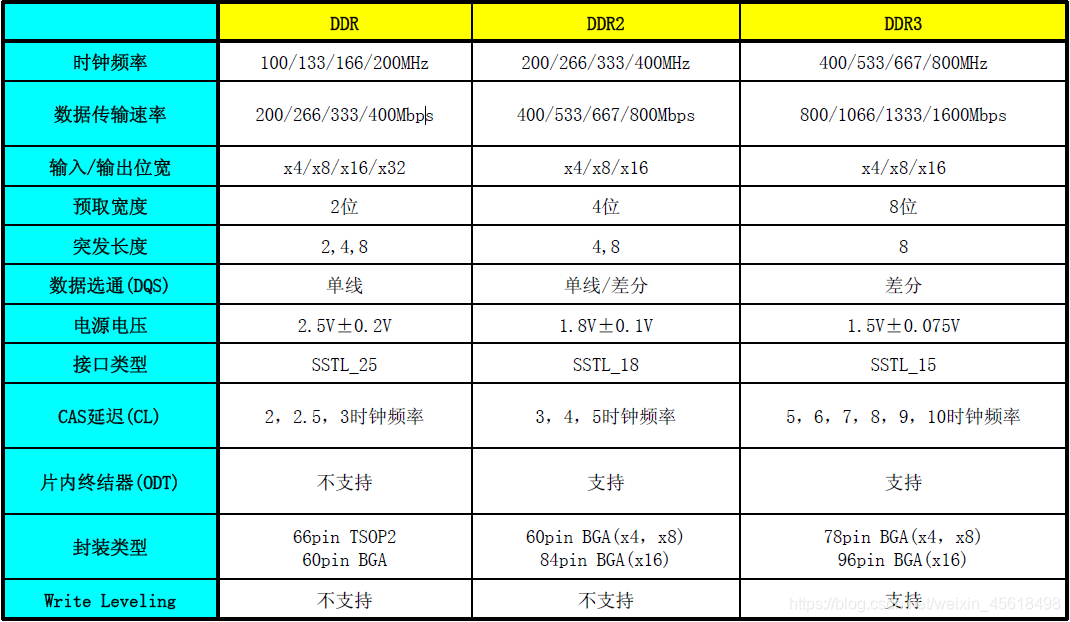

SDRAM從發展到現在已經經歷了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代DDR4 SDRAM。

SDRAM:(Synchronous Dynamic Random Access Memory,同步動態隨機存取記憶體),是在DRAM的基礎上發展而來,為DRAM的一種,同步是指Memory工作需要同步時鐘,內部命令的傳送與資料的傳輸都以時鐘為基準;動態是指儲存陣列需要不斷的重新整理來保證資料不丟失;隨機是指資料不是線性依次儲存,而是由指定地址進行資料讀寫。

下面,我們來了解一下DDR3內部結構。 DDR3的內部是一個儲存陣列,類似於 一張excel表格,有相應的行(row)和列(column),我們可以通過行和列的編號來快速找到我們所需要的格子。而每一張表格我們也對其進行編號,我們稱之為儲存單元,這也就是我們常說的邏輯Bank(L-Bank)。

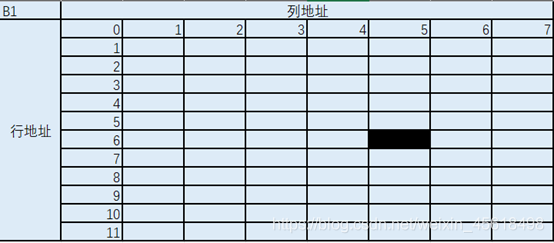

而儲存單元中的每個格點,我們稱之為cell。下圖中黑色格點的地址為B1,R6,C5,如果定址命令為B1,R6,C5,那麼儲存在這個地址中的資料將被讀取出來。

注意:要搞清楚地址和資料的關係。把記憶體看成是一個大倉庫,地址就是小倉庫的門牌號,資料就像存放在倉庫中的貨物。定址就類似通過門牌號找到資料的位置,讀取或寫入資料就類似把貨物從倉庫中取出來或者存進去。

那麼每個cell中的資料量是多少呢,這就涉及到了位寬的概念。DDR的規格一般都會標註x4、x8、x16等字樣,這個x後面的數位就代表DDR晶片的位寬。分別為4bit,8bit,16bit位寬的晶片。晶片中每個cell中儲存的資料量和位寬是相等的,也就是說對於x4、x8、x16規格的晶片,他們內部的每個cell中儲存的資料量分別為4bit,8bit,16bit。

除了邏輯Bank外,DDR3系統還存在物理Bank的概念。也叫做RANK,對SDRAM器件而言,常見的單Die資料位寬為4Bit(x4),8Bit(x8)和16Bit(x16)設定。對於現代的64Bit計算機而言,需要多個SDRAM拼接才可以完成所需的資料位寬。以常見的x8設定的SDRAM顆粒而言,需要8顆晶片拼接完成64Bit的資料位寬,這樣,在Memory controller定址一個資料單元時,8組晶片都會被選中,因此這8組晶片公用一個Cs_n訊號,我們稱之為1個RANK。

二、DDR3容量計算與BANK的理解

DDR容量計算個人認為最簡單的方法就是 地址數x位寬 ,也可以理解為用cell數量x每個cell單元的資料量

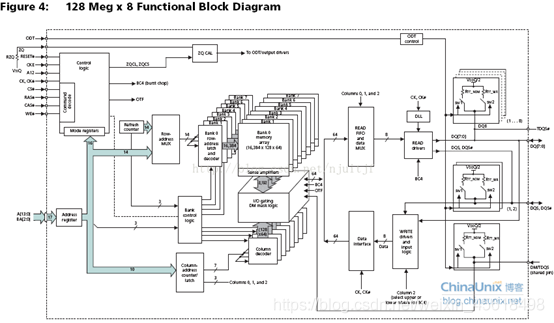

這張圖想必很多人都看到過,這是一顆位寬為8bit的DDR3架構圖,行地址複用線為14根,列地址複用線為10根,Bank數量為8(2^3)。那麼這顆晶片的地址數就為:

2的14次方×2的10次方×2的三次方=128M個地址

128M×8bit=1Gb

因此此晶片儲存的資料量為1Gbit,又因為8bit=1B,所以1Gb=128MB。這也就是我們日常所說的128MB的記憶體條。當然,這張圖片最上面已經標出了128Meg×8,這個128Meg的意思就是此晶片有128M個地址(128M個cell)

然後位寬為8,就可以直接算出來容量的大小。

還有一些標識比如16 Meg x 16 x 8 Banks,這個16Meg則代表的是一個Bank中cell的數量,16為16bit位寬,8為Bank的數量。

像上圖那個8bit位寬的晶片,想要組成一個RANK需要8個晶片組合在一起,也就是組成1GB的記憶體條,CPU可以存取的記憶體大小為1GB。當CPU對記憶體進行存取時,給出一個類似於B1,R6,C5的地址,此時CPU認為只有一塊記憶體,只會給出一個地址,但是拼接起來的8個晶片都會收到此地址,他們會將相應地址中的資料傳出來,每顆晶片傳出8bit資料,八顆晶片共64bit組成一個RANK.

三、DDR3資料傳輸

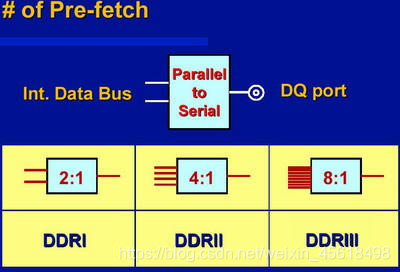

1.預取

DDR一大特點就是預取特性,第一代DDR為2-bit預取,第二代為4-bit預取,第三代為8-bit預取,一些公司將其稱為8-n-Prefetch技術,這裡的8-bit或8-n代表的是8「位」資料,也就是說DDR晶片每次預取的資料量為 8×位寬 個bit,比如一個8bit位寬的DDR3晶片,那麼在每個DDR內部邏輯處理時鐘(此時脈頻率為DDR的核心頻率)的上升沿,都有64bit資料以並行的方式被取出,注意預取時採取的方式是並行,而傳輸時採取的方式為序列。中間經過複雜的並行轉序列結構最後輸出資料,大致意思如下圖所示。

說的簡單一些,假如外部資料位寬8bit,DDR3內部就按8*8的位寬把八個相鄰的資料一次讀出來再並串轉換輸出,所以它內部100MHz就可以達到800MHz的資料率。以此來達到一個提速的目的。

2.傳輸速率

由於計算機現在一個RANK大多為64-bit,所以記憶體條每次傳輸的資料就為64-bit。我們首先把DDR晶片時鐘引腳的頻率稱為工作頻率,而DDR傳輸的方式是在時鐘的上升沿和下降沿各傳輸一次,因此傳輸速率就是工作頻率的二倍,也就是說;

每秒鐘傳輸的次數=工作頻率×2

傳輸的資料量=每秒鐘傳輸的次數×64bit=工作頻率×2×64bit

那麼工作頻率與核心頻率是什麼關係呢,我們通過一個簡單的例子來看一下

就以上面圖中那個8-bit位寬的128MB晶片為例,假設其核心頻率為100MHz,每次預取的資料量為64-bit,但是此晶片共有八根傳輸線,那麼意味著每根傳輸線要以序列的方式在10ns內輸出8-bit資料,由於DDR上升沿和下降沿各傳輸1個bit,那麼只需要在10ns內產生4次時鐘,則此時鐘週期為2.5ns,頻率為400MHz,此頻率就為DDR晶片時鐘引腳的頻率,也就是工作頻率。可以看出:

工作頻率=核心頻率×4

傳輸速率=工作頻率×2=核心頻率×4=核心頻率×預取數

那麼記憶體每秒的資料量是多少呢

拿核心頻率100MHz,位寬8bit的DDR3舉例,八個DDR顆粒組成一個位寬為64bit的記憶體。此條記憶體每次傳輸的資料量都為64bit

傳輸速率=100MHz×8=800M次

也就是說每秒傳輸資料次數為800M次,每次傳輸64bit,那麼總資料量為

總資料量=800M×64bit÷8=6400MBytes=6.4GB

可以看到,核心頻率為100MHz的DDR3的頻寬已經達到6.4GB/s了,可以看出,DDR技術對傳輸速率的提升是十分巨大的。